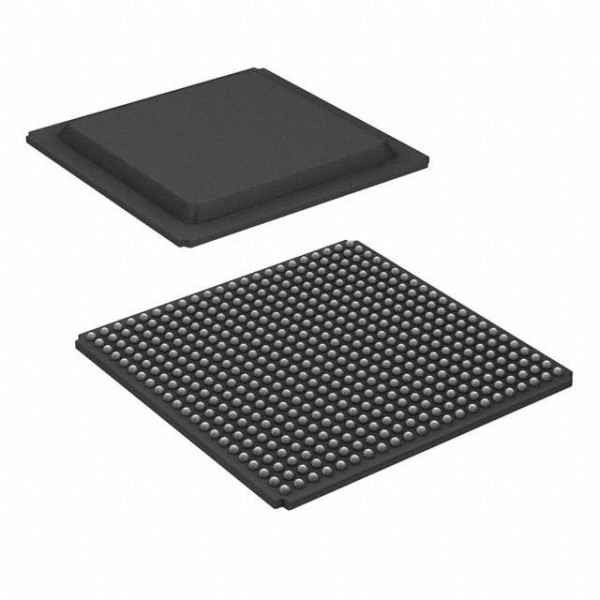

XC6SLX75-2FGG484C フィールドプログラマブルゲートアレイ

♠ 製品説明

| 製品属性 | 属性値 |

| メーカー: | ザイリンクス |

| 製品カテゴリー: | FPGA - フィールドプログラマブルゲートアレイ |

| RoHS指令: | 詳細 |

| シリーズ: | XC6SLX75 |

| ロジック要素の数: | 74637 LE |

| I/O数: | 280 I/O |

| 供給電圧 - 最小: | 1.14V |

| 供給電圧 - 最大: | 1.26V |

| 最低動作温度: | 0℃ |

| 最大動作温度: | + 85℃ |

| データレート: | - |

| トランシーバーの数: | - |

| 取り付けスタイル: | 表面実装 |

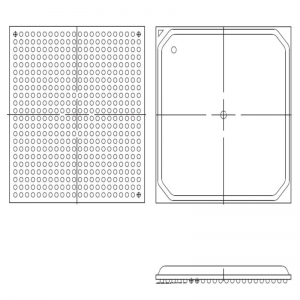

| パッケージ/ケース: | FCBGA-484 |

| ブランド: | ザイリンクス |

| 分散RAM: | 692キロビット |

| 組み込みブロック RAM - EBR: | 3096キロビット |

| 最大動作周波数: | 1080MHz |

| 湿気に敏感: | はい |

| ロジックアレイブロック数(LAB): | 5831 ラボ |

| 動作電源電圧: | 1.2V |

| 製品タイプ: | FPGA - フィールドプログラマブルゲートアレイ |

| 工場パック数量: | 1 |

| サブカテゴリ: | プログラマブルロジックIC |

| 商号: | スパルタン |

| 単位重量: | 1.662748オンス |

♠ Spartan-6ファミリーの概要

Spartan®-6ファミリは、量産アプリケーションにおいて、業界をリードするシステム統合機能と、最も低い総コストを実現します。13製品からなるこのファミリは、3,840~147,443ロジックセルの拡張集積度、従来のSpartanファミリの半分の消費電力、そしてより高速で包括的な接続性を提供します。コスト、消費電力、性能の最適なバランスを実現する成熟した45nm低消費電力銅プロセス技術を基盤とするSpartan-6ファミリは、より効率的な新しいデュアルレジスタ6入力ルックアップテーブル(LUT)ロジックと、豊富なシステムレベルブロックを内蔵しています。これらには、18 Kb (2 x 9 Kb) ブロック RAM、第 2 世代 DSP48A1 スライス、SDRAM メモリ コントローラ、強化された混合モード クロック管理ブロック、SelectIO™ テクノロジ、電力最適化された高速シリアル トランシーバ ブロック、PCI Express® 互換エンドポイント ブロック、高度なシステムレベルの電力管理モード、自動検出構成オプション、AES およびデバイス DNA 保護による強化された IP セキュリティが含まれます。

これらの機能により、カスタムASIC製品に代わる低コストでプログラマブルな代替製品が、これまでにない使いやすさで提供されます。Spartan-6 FPGAは、大量生産ロジック設計、コンシューマ向けDSP設計、そしてコスト重視の組み込みアプリケーションに最適なソリューションを提供します。Spartan-6 FPGAは、統合されたソフトウェアとハードウェアコンポーネントを提供するターゲット設計プラットフォームのプログラマブルシリコン基盤であり、設計者は開発サイクルの開始直後からイノベーションに集中できます。

• Spartan-6 ファミリー:

- Spartan-6 LX FPGA: ロジック最適化

- Spartan-6 LXT FPGA: 高速シリアル接続

• 低コスト設計

- 複数の効率的な統合ブロック

- 最適化されたI/O規格の選択

- ずらしたパッド

- 大容量プラスチックワイヤボンディングパッケージ

• 低い静的および動的電力

- コストと低消費電力に最適化された45nmプロセス

- ゼロ電力の休止状態パワーダウンモード

- サスペンドモードでは、マルチピンウェイクアップ、制御強化により状態と構成を維持します。

- 低消費電力 1.0V コア電圧 (LX FPGA、-1L のみ)

- 高性能 1.2V コア電圧 (LX および LXT FPGA、-2、-3、および -3N 速度グレード)

• マルチ電圧、マルチスタンダードSelectIO™インターフェースバンク

- 差動I/Oあたり最大1,080 Mb/sのデータ転送速度

- 選択可能な出力ドライブ、ピンあたり最大 24 mA

- 3.3Vから1.2VI/Oまでの規格とプロトコル

- 低コストのHSTLおよびSSTLメモリインターフェース

- ホットスワップ対応

- 信号整合性を向上させる調整可能なI/Oスルーレート

• LXT FPGAの高速GTPシリアルトランシーバー

- 最大3.2 Gb/s

- 高速インターフェース: シリアル ATA、Aurora、1G イーサネット、PCI Express、OBSAI、CPRI、EPON、GPON、DisplayPort、XAUI

• PCI Express設計用の統合エンドポイントブロック(LXT)

• 33 MHz、32 ビットおよび 64 ビット仕様と互換性のある低コストの PCI® テクノロジ サポート。

• 効率的なDSP48A1スライス

- 高性能演算および信号処理

- 高速18 x 18乗算器と48ビットアキュムレータ

- パイプラインとカスケード機能

- フィルタアプリケーションを支援する前置加算器

• 統合メモリコントローラブロック

- DDR、DDR2、DDR3、LPDDRのサポート

- 最大800 Mb/sのデータレート(ピーク帯域幅12.8 Gb/s)

- 独立したFIFOを備えたマルチポートバス構造により、設計タイミングの問題を軽減

• ロジック容量の増加による豊富なロジックリソース

- オプションのシフトレジスタまたは分散RAMのサポート

- 効率的な6入力LUTによりパフォーマンスが向上し、消費電力が最小限に抑えられます

- パイプライン中心のアプリケーション向けのデュアルフリップフロップを備えたLUT

• 広範囲の粒度を持つブロックRAM

- バイト書き込み可能な高速ブロックRAM

- オプションで2つの独立した9KbブロックRAMとしてプログラム可能な18Kbブロック

• パフォーマンス向上のためのクロック管理タイル(CMT)

- 低ノイズ、柔軟なクロッキング

- デジタルクロックマネージャ(DCM)はクロックスキューとデューティサイクルの歪みを排除します

- 低ジッタクロック用の位相同期回路(PLL)

- 乗算、除算、位相シフトを同時に行う周波数合成

- 16個の低スキューグローバルクロックネットワーク

• 簡素化された構成、低コストの標準をサポート

- 2ピン自動検出構成

- 幅広いサードパーティ製SPI(最大x4)およびNORフラッシュのサポート

- JTAG 対応機能豊富なザイリンクス プラットフォーム フラッシュ

- ウォッチドッグ保護を使用した複数のビットストリームによるリモートアップグレードのためのマルチブートサポート

• デザイン保護のためのセキュリティ強化

- 設計認証のためのデバイス固有のDNA識別子

- 大型デバイスにおけるAESビットストリーム暗号化

• 強化された低コストの MicroBlaze™ ソフトプロセッサによる組み込み処理の高速化

• 業界をリードするIPおよびリファレンスデザイン